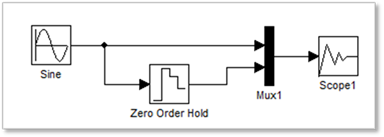

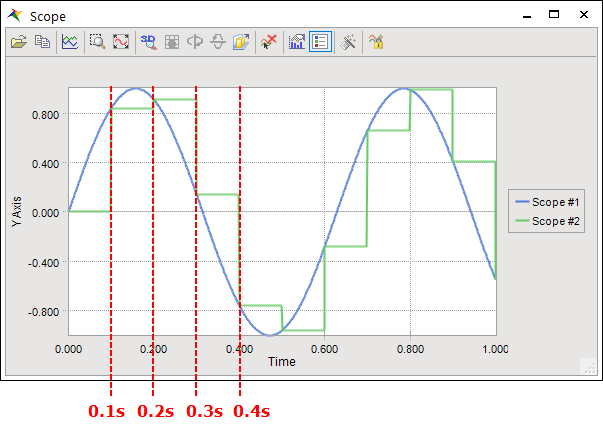

The Zero Order Hold block is a mathematical model of the practical signal reconstruction done by a conventional digital-to-analog converter (DAC). That is, it describes the effect of converting a discrete-time signal to a continuous-time signal by holding each sample value for one sample interval. We can test the DAC with the Colink model shown in the below figure The Sine block is configured to a frequency of 10rad/sec and an amplitude of 1. The Zero Order Hold block Sample time is set to 0.1. Set solver type to Fixed-Step, discrete (no continuous states), and let End time be 1.

Figure 1 colink model

Figure 2 A result from scope